News @ CADET Lab.

[2020/10/30] Prof. Cheng's paper named "A Survey of Test and Reliability Solutions for Magnetic Random Access Memories" was accepted by the prestigious IEEE journal: Proceeings of IEEE. This work was collaborated with researchers from CNRS-LIRMM, Beihang Univ., Delft Univ. of Technology & KIT.

[2020/08/11] Prof. Cheng organized "Chiplet & 3D Integrated Circuits" forum in 1st CCF-DAC conference.

[2020/08/10] Tao's paper titled "A FPGA-based Training Acceleration Framework for Deep Learning Algorithm with the Scalable Template Technique" was accepted by 1st CCF-DAC conference. Congratulations!

[2020/07/14] Baoli's work was nominated as the best post candidate in 2020 CSTIC conference. Congratulations!

[2020/05/17] Prof. Cheng is elevated to IEEE Senior Member.

[2020/3/25] Prof. Cheng attended ISQED'20.

Due to COVID-19, ISQED was changed to a virtual conference. Prof. Cheng atteded on-line and reported the paper "DOVA: A Dynamic Overwriting Voltage Adjustment for STT-RAM L1 Cache".

[2020/2/22] Two papers were accepted by ACM Great Lake Symposium on VLSI 2020.

Papers titled "SIP: Boosting Up Graph Computing by Separating the Irregular Property Data" and "Zero-skew Clock Network Synthesis for Monolithic 3D ICs with Minimum Wirelength" were accepted by GLVLSI'20. Congrats to Jiacheng and Wei !

[2020/2/4] The paper from CADET lab. titled "Write back energy optimization for STT-MRAM based last level cache with data pattern characterization" was accepted by ACM Journal on Emerging Technologies in Computing (JETC).

Congrats to Jiacheng, Jinbo and Keren!

[2020/1/13] Prof. Cheng organized a half-day tutorial: “An Emerging Trend in Post Moore Era: Monolithic 3D IC Technology” on IEEE/ACM ASP-DAC 2020.

[2019/1/10] Prof. Cheng was invited to attend "2020 International Workshop on Advanced Electronic Design Automation" in Xidian University, Xi'an, China.

[2019/12/4] Our paper is accepted by ISQED2020.

Congratulations to Jinbo and Keren!

[2019/11/6] Prof. Chenggang Wu from Institute of Computing Technology was invited by Prof. Cheng to give a talk "SafeHideen:通过持续随机化来确保信息隐藏的高效性和安全性" in CADET group.

[2019/11/4] Prof. Cheng was invited to present the work on 3D IC in Huawei 3D IC workshop, Shenzhen, China.

[2019/9/18] Call for paper of IEEE/ACM ISQED 2020 Conference.

[2019/9/3-2019/9/4] Prof. Cheng attended the 1st IEEE/ACM Machine Learning on CAD workshop in Canmore, Canada.

[2019/8/20] Call for paper of IEEE/ACM DATE 2020 Conference.

[2019/8/19] Prof. Cheng was invited to give a talk "Low Power and Reliable Design for Emerging Technologies" on IEEE NVMSA 2019 conference, Hangzhou, China.

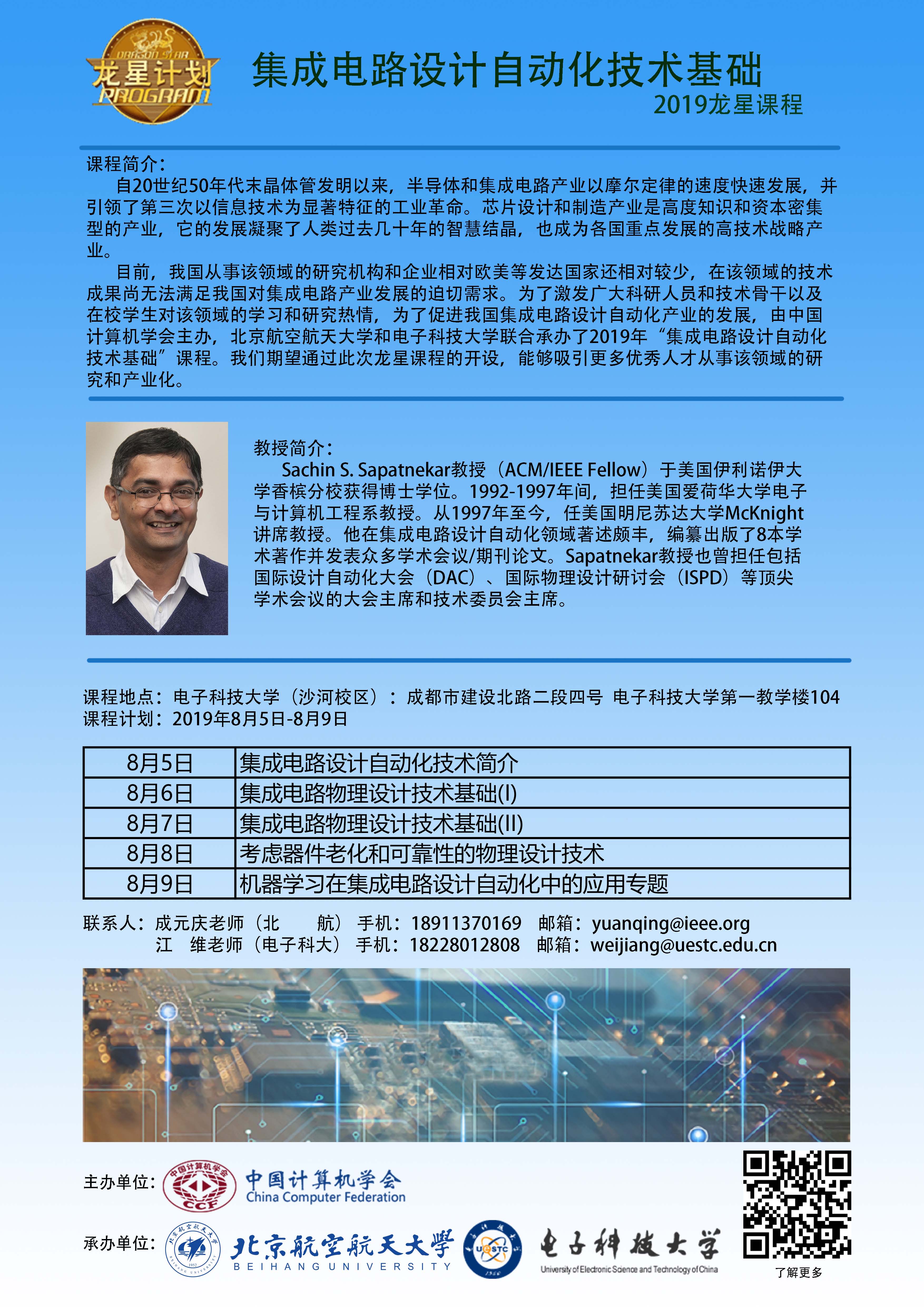

[2019/7/20] CCF Dragon Star Course "Introduction to Design Automation of VLSI" will start in UESTC, Chengdu.

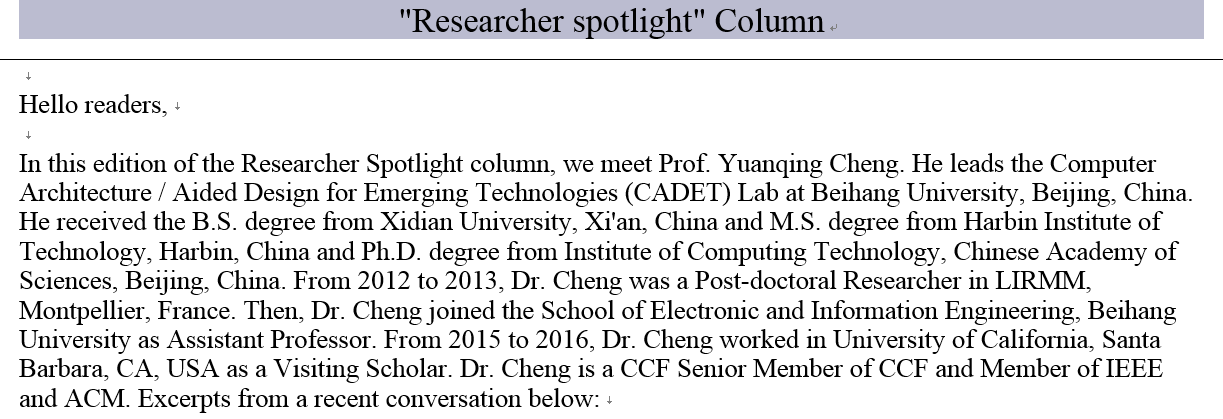

[2019/6/1] The research of CADET group led by Prof. Cheng was reported by ACM SIGDA

[2019/4/21] Prof. Cheng's paper was accepted by TVLSI

The paper titled "An Adaptive Thermal-Aware ECC Scheme for Reliable STT-MRAM LLC Design" was accetped by IEEE Transactions on Very Large Scale Integration (VLSI) Systems. This work is collaborated with Bi Wu from Prof. Weisheng Zhao's group, and Prof. Ying Wang from Institute of Computing Technology, Chinese Academy of Sciences.

[2019/3/25-2019/3/29] Prof. Cheng attended DATE 2019 conference

Prof. Cheng was invited as the chair of session "Learning gets smarter" in DATE 2019 held in Florence, Italy. DATE conference is one of the premier EDA conferences, which attracts more than 1000 researchers and engineers to attend every year.

[2019/2/10] Prof. Cheng's paper was accepted by IEEE Trans. on CAD

The paper titled "A Novel High Performance and Energy Efficient NUCA Architecture for STT-MRAM LLCs with Thermal Consideration" was accepted by IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems. This work is collaborated with Bi Wu from Prof. Weisheng Zhao's group, and Prof. Ying Wang from Institute of Computing Technology, Chinese Academy of Sciences.

[2019/1/5] New funding: from Beijing Natural Science Fundation.

The proposal "Multi-failure Mechanism Reliability Modeling and Reliable Design for STT-MRAM" gets supported by Beijing Natural Science Fundation with Grant No. 4192035.

[2018/11/1] Prof. Vasilis Pavlids visited CADET lab. for academic collaborations.

Prof. Pavlids from University of Manchester visited CADET lab. The visit is to enhance the collaborations between Prof. Pavlids's group and CADET on the research of monolithic 3D ICs. He will give a five-day short course on 3D IC design during stay in Beihang University.

[2018/9/1] New funding: Key project of "111" plan.

The proposal titled "Monolithic 3D Integrated Circuit Design with Spintronic Technology was supported by Beihang University with grant No. Z2018004.. The proposal is based on the collaboration between CADET team and the team led by Prof. Vasilis Pavlids from University of Manchester, U.K.

[2018/6/24] Prof. Cheng attened DAC'2018.

The paper of CADET titled "An Adaptive Thermal-Aware ECC Scheme for Reliable STT-MRAM LLC Design", collaborating with Bi Wu from Prof. Weisheng Zhao's group, was selected as Work-In-Progress poster on DAC'2018. Prof. Cheng presented this work and took a photo with David Patterson - the 2018 ACM Turing Award winner:)

[2018/5/28] Prof. Cheng and student Chen Liu attended ISCAS'2018.

Chen Liu from CADET Lab. presented our group's paper titled "NEAR: a Novel Energy Aware Replacement Policy for STT-MRAM LLCs" on ISCAS'2018 conference.

[2018/5/9] Prof. Cheng's paper was accepted by ISVLSI 2018.

The paper of Prof. Cheng's group collaborated with Prof. Weisheng Zhao's group titled "Write energy optimization for STT-MRAM cache with data pattern characterization" was accepted by ISVLSI 2018 conference.

[2018/2/21] Wu's paper was accepted as DAC'18 WIP.

Bi Wu's paper titled "Chameleon: A Thermally Adaptive Error Correction Code Design for STT-MRAM LLCs" was accepted as Work-in-Progress poster of Design Automation Conference 2018. Congratulations to Bi!

[2018/2/9] Prof. Cheng's paper was accepted by TNANO.

Prof. Yuanqing Cheng's paper, collaborated with Mr. Liuyang Zhang and Prof. Aida Todri-Sanial, titled "Addressing the Thermal Issues of STT-MRAM from Compact Modeling to Design Techniques" was accepted by IEEE Transactions on Nanotechnology.

[2018/1/25] Chen's paper was accepted by ISCAS'18.

Chen Liu's paper titled "NEAR: a Novel Energy Aware Replacement Policy for STT-MRAM LLCs" was accepted by 2018 IEEE International Symposium on Circuits and Systems, to be held in Florence, Italy from May 27-30. Congratulations to Chen Liu! Good job!

[2017/12/19] Prof. Cheng's paper was accepted by JSCT.

Prof. Yuanqing Cheng's paper titled "Power Supply Noise Aware Task Scheduling on Homogeneous 3D MPSoCs Considering the Thermal Constraint" was accepted by Journal of Computer Science and Technology, Springer.

[2017/11/18] Our group's paper was accepted by TVLSI.

Our group's paper, collaborated with Ms. Linuo Xue and Prof. Yuan Xie, titled "An Adaptive 3T-3MTJ Memory Cell Design for STT-MRAM based LLCs" was accepted by IEEE Transactions on Very Large Scale Integrated Systems. Congratulations to Bi Wu and Beibei!

[2017/9/13] Bi winned the National Scholarship.

Bi Wu wins the National Scholarship. Congratulations to Bi Wu!

[2017/6/27] Our paper was accepted by ICCAD'17.

Our paper titled "Thermosiphon: A Thermal Aware NUCA Architecture for Write Energy Reduction of the STT-MRAM based LLCs" is accepted by ICCAD conference. Congratulations to Bi Wu!